��Ҫ����ijЩ����������ʵЧ��(����)�Ĺ��ջ��ڣ�����Ҫ�����������ַ�����������RAM����������ROM��

(2)�������뷽��

���ַ������ڴ洢оƬ�ڲ����þ������룬�Զ���Ⲣ�������˷�������Ҫ����IJ��Ժ;�������ȹ��ջ��ڣ�����߳�Ʒ���⣬���Կɿ��������ԸĽ������ַ�����ͻ�����ŵ����ر��ʺ�ROM���ڶ��ٶ�Ҫ�ߵ������Ҳ������RAM��������Ҫȱ������Ҫռ�ö����оƬ�����ͬʱ��������Ӱ��оƬ�����Ĺ����ٶȡ������ڴ洢��ϵͳ���ľ���������ݴ���������洢��оƬ�ڲ�������ߴ洢оƬ��Ʒ�ʺͿɿ��Ե���Ч��ʩ�������������ʹ�õ�ECC�ڴ�Ͳ����˴˼�����

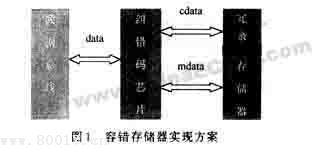

���ĵ��ݴ��洢�����þ����뷽������ʵ�ֿ�ͼ��ͼ1��ʾ��

2��2���������·���

2��2���������·���

�������·�������CPU�Ķ�дʱ����й��������Խ�CPU��ʱ���Ϊ�����ں�д���ڡ���д����ʱ������ͨ��������·ֱ�ӽ�����д�뵽�洢����ͬʱ����ͨ��������·����5 bУ����д�뵽����洢����������ʱ�ֳ�2������1���Ӵ洢��������洢���ֱ��ȡ���ݺ�У��λ�������������·���棻��2�����м�������û�д���ֱ�ӽ������ͳ����������ߣ���2λ�������жϽ��д�������1λ�������ݽ��о����������������ߡ�����Ҫ������ȷ���ݣ������У��λ���������κδ�����ֱ�������ȷ���ݡ�

2��3����·����������

RD��WR��CLKΪCPU���뵽������źţ�ͨ�����Ƶ�·����оƬ�ڿ����źš���д�ź�ʱ��DB��7����0�ݴ������������룬ͨ�������Ժ���̬����(Santaiģ��)д�뵽�洢����ͬʱ����ͨ��У�������ģ��(Paritygen)����5 bУ���룬ͨ����̬����д������洢�������ź�ʱ���洢�����ݶ���������·������������5 bУ���룬ͬʱ�������洢�������5 b������һ��ͨ������ͼ��ģ��(Errorsample)����������ͼ����ͨ������ͼ�����������ݲ�������ʱͨ

����������ȫ�������DZ�MRO��_������http://www.80017.cn/ �ṩ��

ע:�����ĵ��Բ�����ֱ������,���Ҽ�����������ֻ�'�������'ͼ��,Ȼ��ѡĿ������Ϊ,�������ر���

(������Դ��ȫ�������DZ�MRO��_������)

- ��һƪ�����DZ��������£� һ�����ͷ���ʧ�Դ洢����ԭ����Ӧ��

- ��һƪ�����DZ��������£� IDT70V9289����ͬ��˫��SRAM��ԭ����Ӧ��

| ǯ�ε�������ʹ�÷��� | 5��11�� |

| ��Яʽ�������ǵ�ʹ�÷��� | 5��11�� |

| ʲô��ҵ�ʺ�ʹ�ú�������� | 5��10�� |

| ���ߴ���������Զ��ҽ�Ƽϵ | 5��10�� |

| ����ѡ����ӳӳ��ش����� | 5��3�� |

| ��������ǵ�Ӧ�� | 5��2�� |

| ����������Ӧ������6���ص� | 5��2�� |

| ʾ����ʹ���ߵ��������⣬ | 5��2�� |

| ��ν��������·�ֹ��� ��»�� | 4��27�� |

| ��»����������н����Ĵ����� | 4��27�� |

| ���ñ���β������ | 5��2�� |

| ͭоͭ��������þ��Ե������� | 5��20�� |

| ���ʵ�������������֮��� | 4��20�� |

| AWG��mm���� | 4��6�� |

| ����ճ�ȵ�λ����� | 5��20�� |

| ��ο��ٿ�����·ͼ | 5��20�� |

| ���µĺ��ӱ� | 5��20�� |

| Ʒ �� �� �� ֪ �R | 5��20�� |

| ��Ӱ������Ѳ������ | 5��2�� |

| �����DZ�ѧ��:һ�����͵���鵥 | 4��12�� |

���������������ip4��iP2

���������������ip4��iP2