����CPLD���ݴ��洢�������ʵ��

���ߣ�ȫ��MRO�ۺϷ����� �����DZ�����������Դ��ȫ��MRO�����DZ������� ������� ����ʱ�䣺2006-10-11

������ģ��(Errorcorrect)��������ȷ����������������ߡ�ErrordetecΪ����״̬ģ�飬SEF��DEFΪ����״̬�źš�0��0ʱ����1��0ʱ1λ����1��1ʱ2λ������·ʵ�ֵĸ����ֹ���ģ����ͼ2��ʾ����

3�����漰�䲨��

3�����漰�䲨��

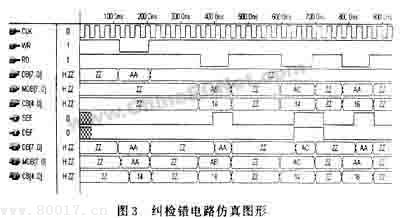

���IJ���Altera��˾��CPLD����EPM7128��Ϊ��ƻ��� ��5�� ��ͼ3�Ǿ������·����ͼ�Σ���CPLDʵ�־������·���棬ͼ��118��205 nsʱ����������д������AA��359��443 nsʱ�����˶�����ʱ����1λ�������601��692 nsʱ�����˲���2λ���������ʱ����2λ�������Dz��ܾ�����781��863 nsʱ������У��λ����1λ��ʱ�������

4�����������

4�����������

�������������Ȩ��Ļ���ԭ����Ƶľ������·����У����λ�������2λ�����洢������λ�����жϹ���������ƽ������ʱ��MTBF��������˿ɿ��ԡ����Ǿ�һ����������������ʹMTBF�����½���

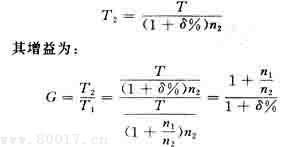

��Ч���ϣ�����ʱ��T�ڣ�����1λ���Ĵ���Ϊn 1 ������2λ����λ���Ĵ���Ϊn 2 �����þ�����ʱ��ƽ������ʱ��ΪT 1 ��T/(n 1 ��n 2 )�����������Ȩ���1λ���ǿɾ��ģ���2λ����λ���Dz��ɾ��ģ���Ϊ���������������ڲ��þ�������������Ħģ���������������Ȩ����ƽ������ʱ��Ϊ��

�����Ϲ��ƣ�����1λ��ռ

�����Ϲ��ƣ�����1λ��ռ

����������ȫ�������DZ�MRO��_������http://www.80017.cn/ �ṩ��

ע:�����ĵ��Բ�����ֱ������,���Ҽ�����������ֻ�'�������'ͼ��,Ȼ��ѡĿ������Ϊ,�������ر���

(������Դ��ȫ�������DZ�MRO��_������)

- ��һƪ�����DZ��������£� һ�����ͷ���ʧ�Դ洢����ԭ����Ӧ��

- ��һƪ�����DZ��������£� IDT70V9289����ͬ��˫��SRAM��ԭ����Ӧ��

| ǯ�ε�������ʹ�÷��� | 5��11�� |

| ��Яʽ�������ǵ�ʹ�÷��� | 5��11�� |

| ʲô��ҵ�ʺ�ʹ�ú�������� | 5��10�� |

| ���ߴ���������Զ��ҽ�Ƽϵ | 5��10�� |

| ����ѡ����ӳӳ��ش����� | 5��3�� |

| ��������ǵ�Ӧ�� | 5��2�� |

| ����������Ӧ������6���ص� | 5��2�� |

| ʾ����ʹ���ߵ��������⣬ | 5��2�� |

| ��ν��������·�ֹ��� ��»�� | 4��27�� |

| ��»����������н����Ĵ����� | 4��27�� |

| ���ñ���β������ | 5��2�� |

| ͭоͭ��������þ��Ե������� | 5��20�� |

| ���ʵ�������������֮��� | 4��20�� |

| AWG��mm���� | 4��6�� |

| ����ճ�ȵ�λ����� | 5��20�� |

| ��ο��ٿ�����·ͼ | 5��20�� |

| ���µĺ��ӱ� | 5��20�� |

| Ʒ �� �� �� ֪ �R | 5��20�� |

| ��Ӱ������Ѳ������ | 5��2�� |

| �����DZ�ѧ��:һ�����͵���鵥 | 4��12�� |

���������������ip4��iP2

���������������ip4��iP2